About us

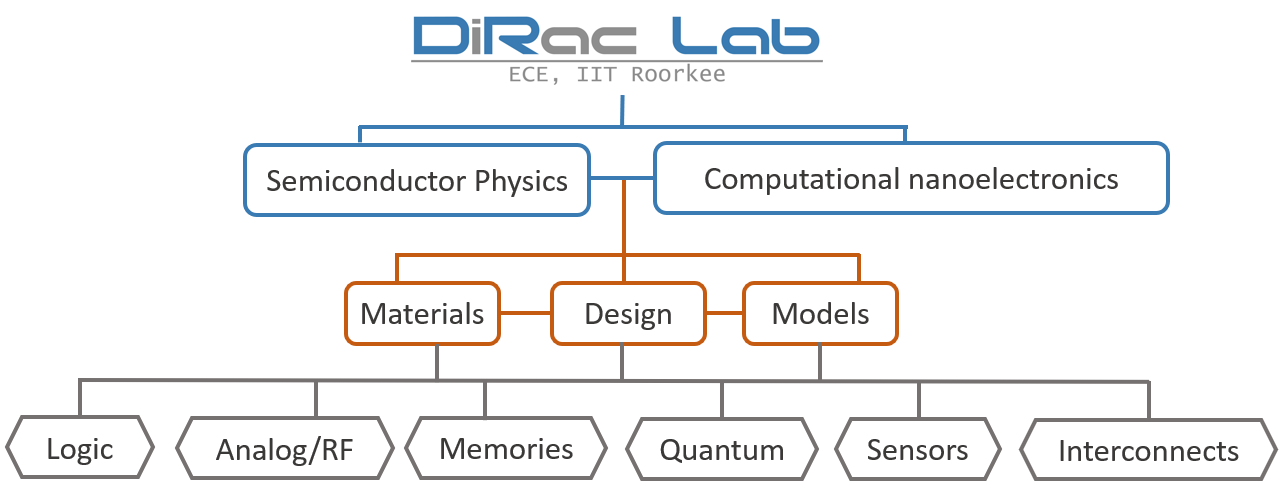

DiRac Lab is the hub of all research activities related to semiconductor devices in the department of Electronics and Communication Engineering, IIT Roorkee. We work on all aspects of semiconductor devices starting from material physics through device design and modeling, all the way to device-circuit co-design for a wide variety of applications.

Announcements

- Surila has successfully defended her Ph.D. thesis and has recently joined Micron, India.

- We are presenting presenting our work on advanced ANN algorithm for device modeling in TECHCON (USA), 2024.

- We are presenting presenting our work on uncertainty quantification for interconnects in EMC (USA), 2024.

- Prabhat has received the SERB International Travel Grant, 2024.

- Abhishek has received the SERB International Travel Grant, 2024.

- Srishti and Abhishek have received the prestigious Prime Minister's Research Fellowship in 2023.

- Kumar Sheelvardhan has received the prestigious Prime Minister's Research Fellowship in 2023.

- We are working with Lancaster University on novel memory devices

- We are working with Semiconductor Research Corporation on Machine Learning augmented Compact Models

- We are working with GlobalFoundries on exploratory topics in Non-Volatile Memory and Machine Learning.

Contact Us

Reach out to DiRac Lab

Location:

W-202/1,

Department of Electronics and Communication Engineering,

Indian Institute of Technology Roorkee

Email:

diraclab@ece.iitr.ac.in